**User Manual**

# Tektronix

**Tektronix Logic Analyzer Family Version 4.2 Software**

071-0863-02

Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., 14200 SW Karl Braun Drive, Beaverton, OR 97077

TEKTRONIX, TEK, and MagniVu are registered trademarks of Tektronix, Inc.

#### HARDWARE WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### SOFTWARE WARRANTY

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on the media will be free from defects in materials and workmanship for a period of three (3) months from the date of shipment. If a medium or encoding proves defective during the warranty period, Tektronix will provide a replacement in exchange for the defective medium. Except as to the media on which this software product is furnished, this software product is provided "as is" without warranty of any kind, either express or implied. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and workmanship within a reasonable time thereafter, Customer may terminate the license for this software product and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

|                         | General Safety Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                          | xvi                                                         |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                         | Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | xi<br>x                                                     |

|                         | Terms Used in this Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XX<br>XX                                                    |

|                         | Contacting Tektronix                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xxiv                                                        |

| Getting Started         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |

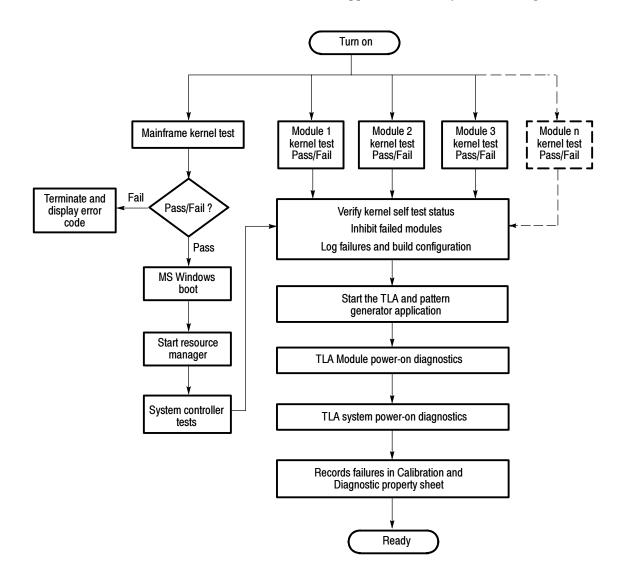

|                         | TLA600 Series Logic AnalyzersTLA700 Series Logic AnalyzersAccessoriesInstallationInstalling Expansion MainframesInstalling TLA700 ModulesConnecting AccessoriesConnecting ProbesFirst Time OperationTurning On the TLA600 Series Logic AnalyzerTurning On the TLA700 Series Logic AnalyzerPowering On the MainframesTurning Off the TLA700 Series MainframePerforming the Incoming InspectionBacking Up User FilesRemoving the Replaceable Hard Disk Drive (TLA700 Series Only) | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                     |

|                         | Connecting Probes to the Target System                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-2<br>1-2                                                  |

| <b>Operating Basics</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-3                                                         |

| e pera mig zueree       | Functional OverviewFront Panel ControlsTLA600 Series External ConnectorsTLA600 Series Chassis Ground ConnectionsTLA700 Series External ConnectorsTLA700 Series Chassis Ground ConnectionsTLA700 Series Chassis Ground Connections                                                                                                                                                                                                                                               | <b>2-1</b><br>2-2<br>2-3<br>2-5<br>2-6                      |

|                         | Approaching the TLA Application Windows                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-9                                                         |

|                         | System Window<br>Setup Windows<br>Trigger Windows<br>Data Windows<br>MagniVu Data<br>Saving and Loading Setups and Data<br>Customizing the Display<br>Programmatic Control                                                                                                                                                                                                                                                                                                      | 2-9<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1 |

|                         | Approaching the Pattern Generator Application WindowsSystem Window                                                                                                                                                                                                                                                                                                                                                                                                              | <b>2-2</b>                                                  |

| Setup Windows                                 | 2-22 |

|-----------------------------------------------|------|

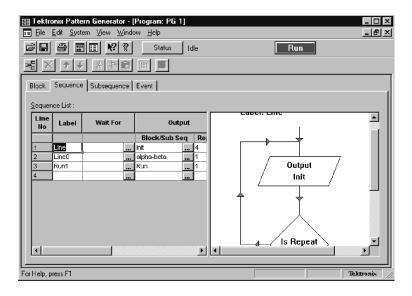

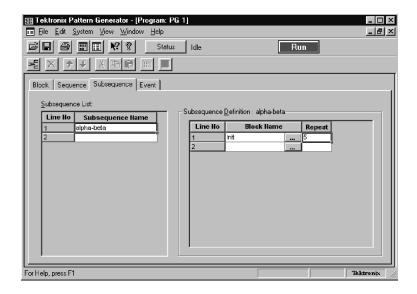

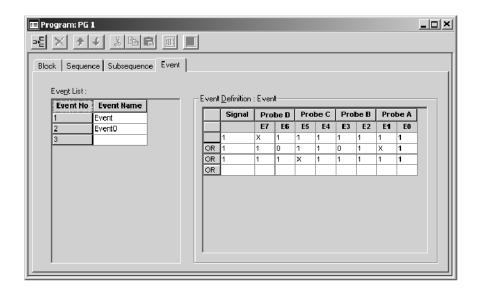

| Program Window                                | 2-23 |

| PG Run Properties Dialog Box                  | 2-26 |

| Operating Basics                              | 2-27 |

| Sampling and Digitizing a Signal              | 2-27 |

| LA Module Block Diagram                       | 2-28 |

| DSO Module Block Diagram                      | 2-30 |

| Pattern Generator Module Block Diagram        | 2-31 |

| Logic Analyzer Physical Model                 | 2-33 |

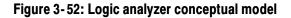

| Logic Analyzer Conceptual Model               | 2-33 |

| Intermodule Interactions and Time Correlation | 2-34 |

| Listing-Data Concepts                         | 2-35 |

| Microprocessor Support                        | 2-36 |

| High-Level Language (Source Code) Support     | 2-37 |

| Waveform Data Concepts                        | 2-39 |

| Performance Analysis Concepts                 | 2-45 |

| Comparing Acquired Data Against Saved Data    | 2-46 |

| Repetitive Acquisitions                       | 2-47 |

| Symbol Support                                | 2-48 |

|                                               |      |

## Reference

| Setup                                         | 3-1  |

|-----------------------------------------------|------|

| Starting From the System Window               | 3-1  |

| Setting Up the LA Module                      | 3-3  |

| Setting Up the Trigger Program                | 3-28 |

| Setting Up the DSO Module                     | 3-52 |

| Setting Up the External Oscilloscope          | 3-57 |

| Setting Up the Pattern Generator Module       | 3-60 |

| Setting Up the Pattern Generator Program      | 3-63 |

| System Trigger                                | 3-68 |

| Arming Modules                                | 3-70 |

| Intermodule and External Signaling            | 3-71 |

| Merging Modules                               | 3-73 |

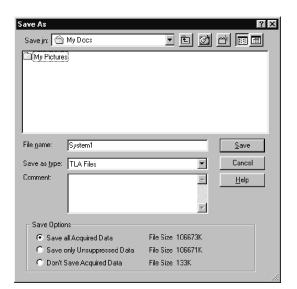

| Saving and Loading Setups, Triggers, and Data | 3-75 |

| System Options                                | 3-79 |

| Menu Shortcut Keys                            | 3-80 |

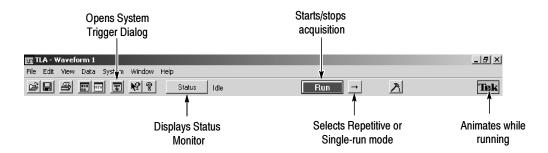

| Acquisition                                   | 3-81 |

| Starting and Stopping Acquisition             | 3-81 |

| Viewing Acquisition Activity                  | 3-83 |

| If the Logic Analyzer Does Not Trigger        | 3-84 |

| Display                                       | 3-87 |

| Opening an Existing Data Window               | 3-88 |

| Opening a Saved Data Window                   | 3-89 |

| Aligning Saved Data with Current Data         | 3-89 |

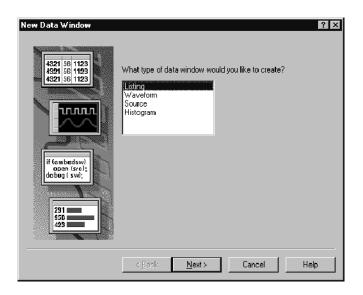

| Creating a New Data Window                    | 3-90 |

| General Purpose Data Window Shortcut Keys     | 3-91 |

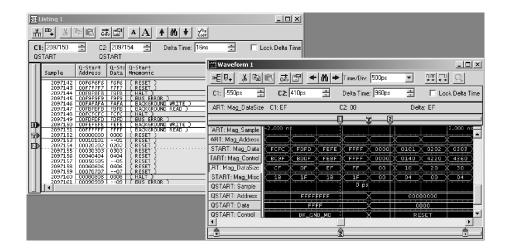

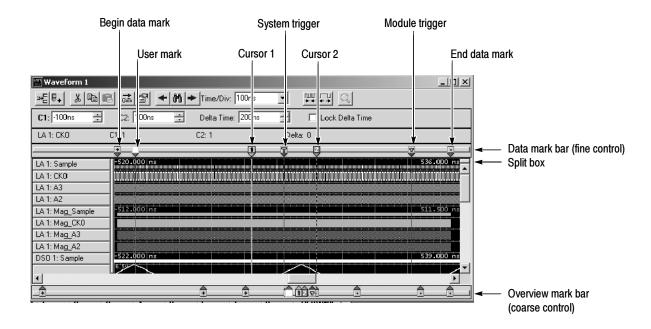

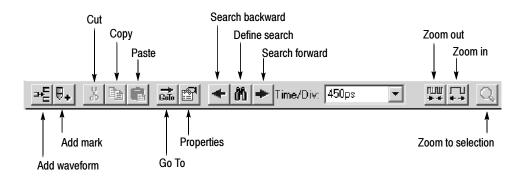

| Waveform Window                               | 3-93 |

| Types of Waveforms                            | 3-94 |

| Reading the Waveform Indicators               | 3-96 |

| Zoom Box                                      | 3-97 |

| Taking Cursor Measurements                 | 3-98  |

|--------------------------------------------|-------|

| Automatic Waveform Measurements            | 3-99  |

| Jumping to Specific Data Locations         | 3-102 |

| Searching Data                             | 3-104 |

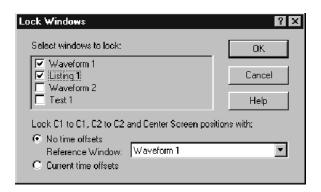

| Locking Windows                            | 3-105 |

| MagniVu Data                               | 3-106 |

| Changing Analog Multiplex Data             | 3-108 |

| Comparing Waveform Data                    | 3-110 |

| Adjusting the Waveform Window              | 3-112 |

| Customizing the Waveform Window Data       | 3-115 |

| Exporting Waveform Data                    | 3-115 |

| Waveform Window Shortcut Keys              | 3-116 |

| Overlay Waveforms                          | 3-116 |

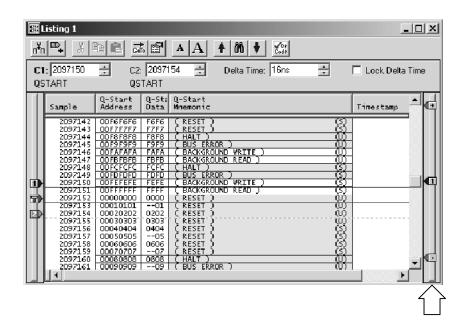

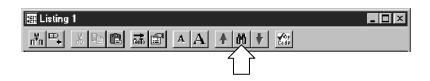

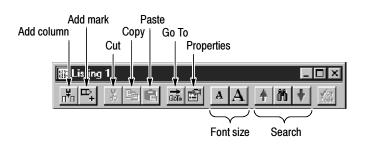

| Listing Window                             | 3-119 |

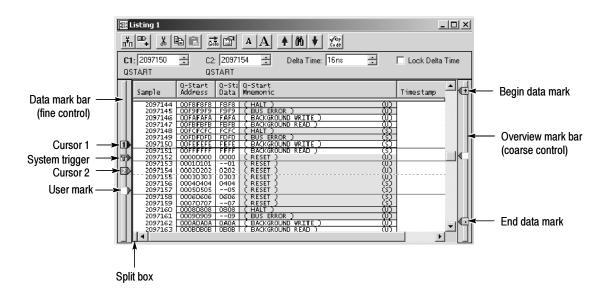

| Reading the Listing Window Indicators      | 3-119 |

| Taking Cursor Measurements                 | 3-119 |

|                                            | 3-121 |

| Jumping to Specific Data Locations         | 3-121 |

| Searching Data                             | 3-123 |

| Locking Windows                            | 3-124 |

| Comparing Listing Data                     | 3-124 |

|                                            | 3-123 |

| Adjusting the Listing Window               | 3-12/ |

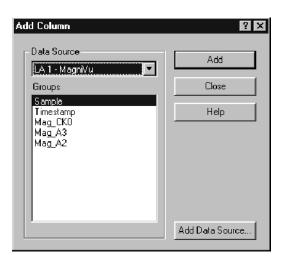

| Customizing the Listing Window Data Area   | 3-129 |

| Exporting Listing Data                     | 3-130 |

| Listing Window Shortcut Keys               |       |

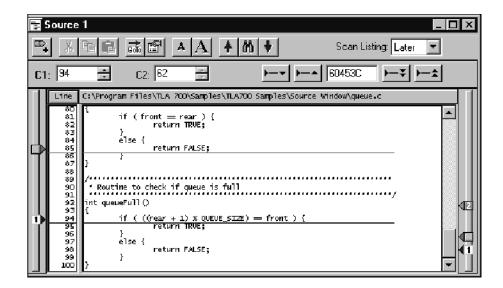

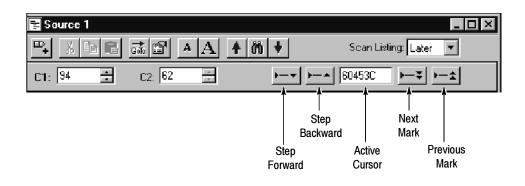

| Source Window                              | 3-135 |

| Creating a Source Window                   | 3-136 |

| Reading the Source Window Indicators       | 3-136 |

| Jumping to Specific Data Locations         | 3-137 |

| Moving Through Source Files                | 3-138 |

| Searching for Source Data                  | 3-141 |

| Adjusting the Source Window                | 3-142 |

| Customizing the Source Window Data Area    | 3-142 |

| Locating Source Files                      | 3-143 |

| Source Window Shortcut Keys                | 3-145 |

| Histogram Window                           | 3-147 |

| Measuring Histogram Data                   | 3-148 |

| Creating a Histogram Window                | 3-140 |

| Adjusting the Histogram Window             | 3-149 |

| Customizing the Histogram Window Data Area | 3-150 |

| Exporting Histogram Data                   | 3-151 |

| Histogram Window Shortcut Keys             | 3-152 |

|                                            | 0 100 |

## Appendices

| Appendix A: Specifications                                          | A-1  |

|---------------------------------------------------------------------|------|

| Characteristic Tables                                               | A-1  |

| Atmospheric Characteristics for the Tektronix Logic Analyzer Family | A-2  |

| Certifications and Compliances                                      | A-3  |

| TLA600 Series Logic Analyzer Specifications                         | A-5  |

| TLA700 System Specifications                                        | A-17 |

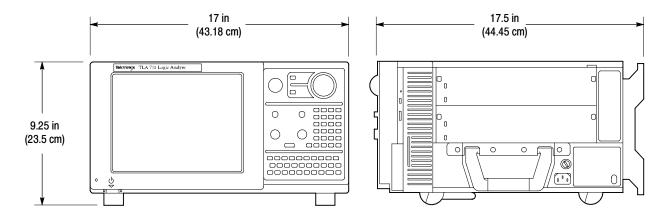

| TLA715 Dual Monitor Portable Mainframe Characteristics              | A-23 |

|                                                                     |      |

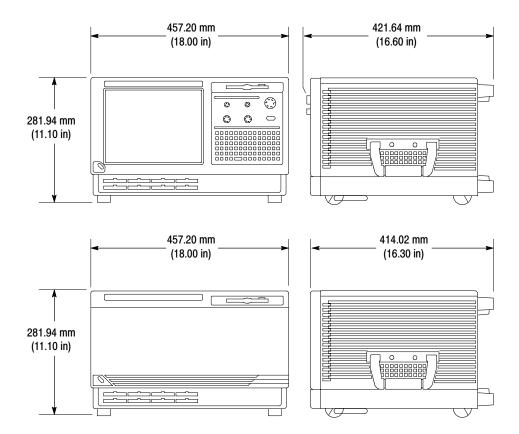

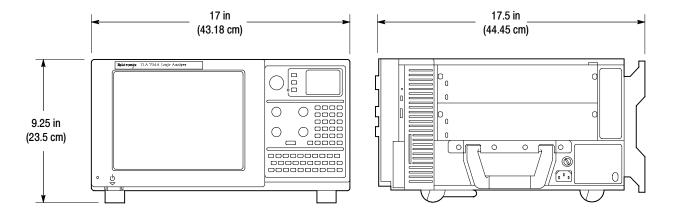

| TLA714 Portable Mainframe Characteristics                  | A-29        |

|------------------------------------------------------------|-------------|

| Benchtop and Expansion Mainframe Characteristics           | A-34        |

| TLA721 Dual Monitor Benchtop Controller Characteristics    | A-39        |

| TLA720 Benchtop Controller Characteristics                 | A-42        |

| TLA7Axx Series Logic Analyzer Module Characteristics       | A-44        |

| TLA7Lx/Mx/Nx/Px/Qx Module Characteristics                  | A-54        |

| DSO Module Characteristics                                 | A-61        |

| TLA7PG2 Pattern Generator Module Characteristics           | A-67        |

| External Oscilloscope (iView) Characteristics              | A-70        |

| Appendix B: TLA Symbol File Format                         | <b>B-1</b>  |

| TSF Headers                                                | B-2         |

| TSF Pattern Symbols                                        | B-3         |

| TSF Range Symbols                                          | <b>B-</b> 4 |

| Appendix C: Pattern Generator Physical-Logical Conversion  | C-1         |

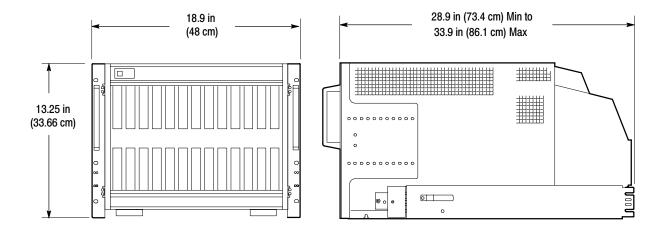

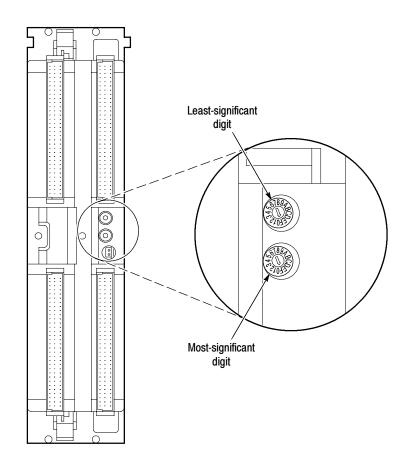

| Appendix D: TLA700 Module Installation                     | <b>D-1</b>  |

| Setting the Logical Address                                | <b>D-</b> 1 |

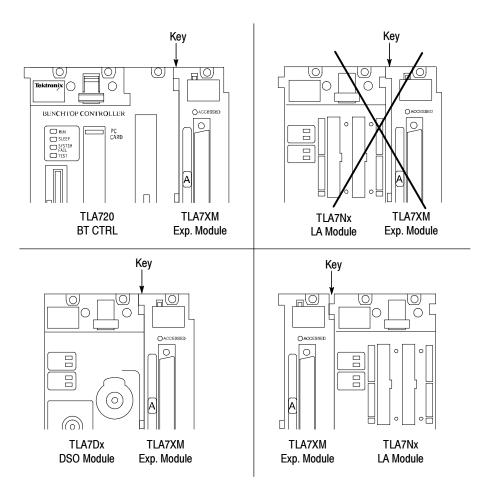

| Merging Modules                                            | D-2         |

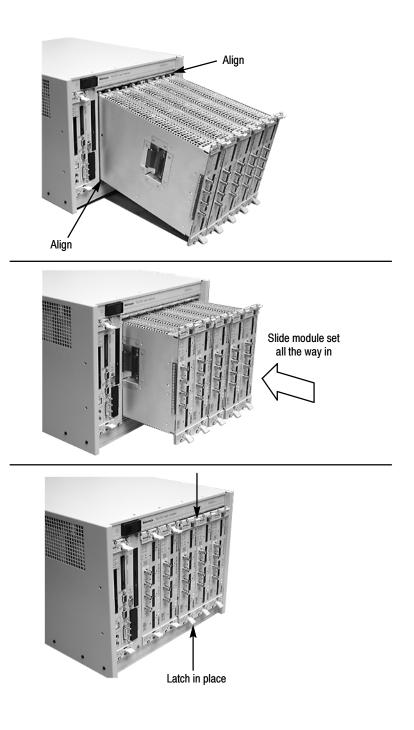

| Installing Modules in the Portable Mainframe               | D-3         |

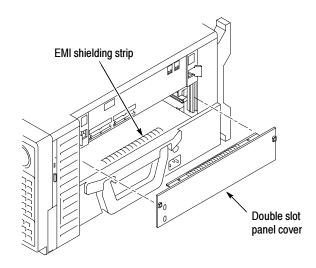

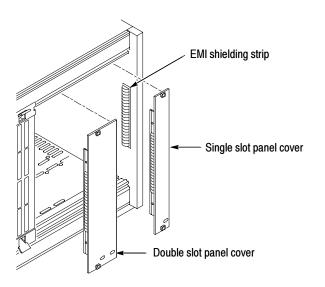

| Installing Modules in the Benchtop or Expansion Mainframes | D-3         |

| Module Keying                                              | D-5         |

| Covering Empty Slots                                       | D-5         |

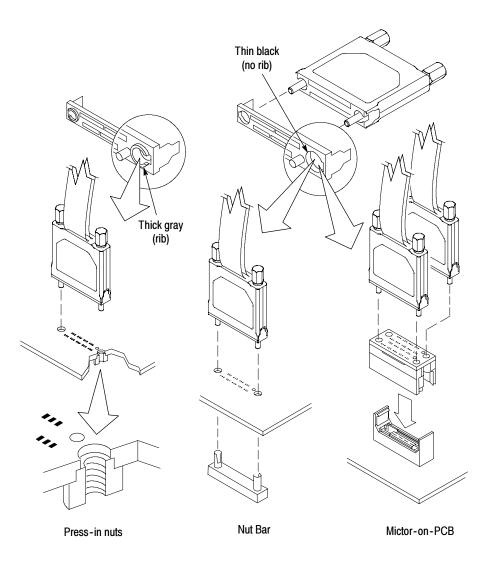

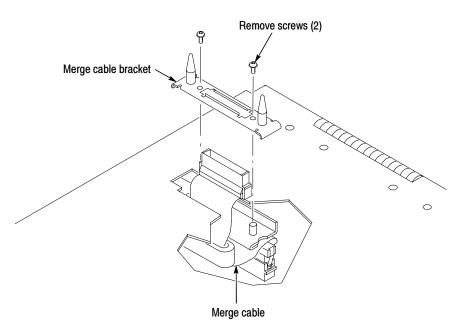

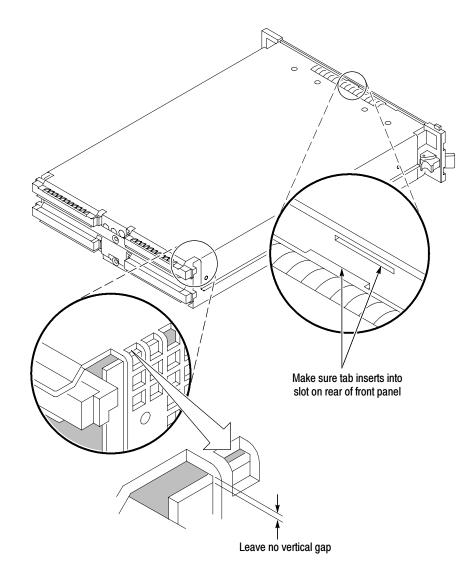

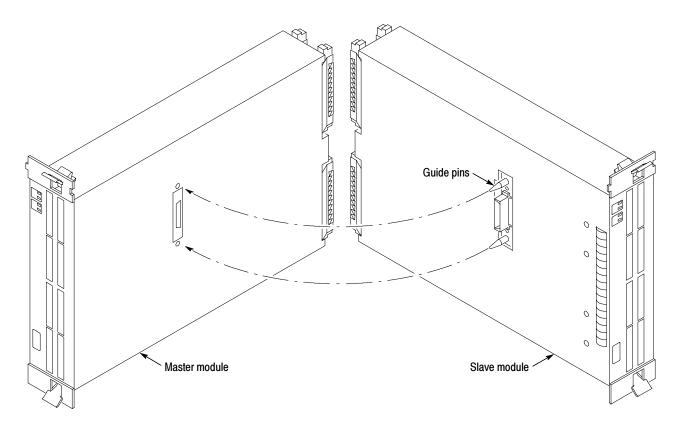

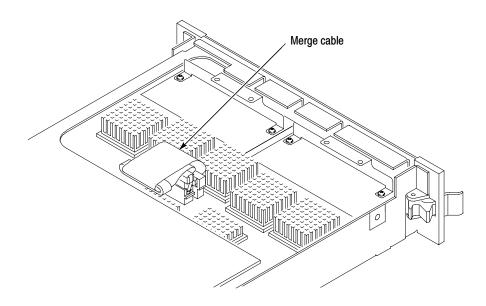

| Appendix E: Merging Modules                                | <b>E-1</b>  |

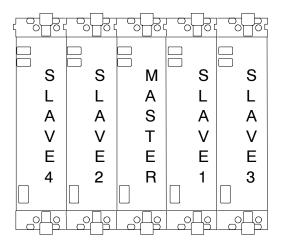

| Logic Analyzer Module Merging Rules                        | E-1         |

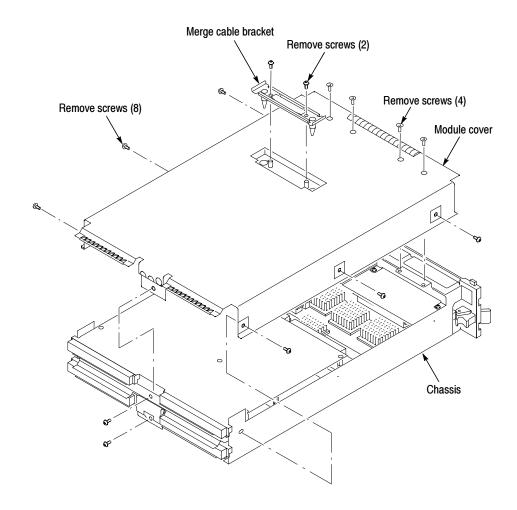

| Merge Procedure                                            | E-2         |

| Pattern Generator Module Merging Rules                     | E-3         |

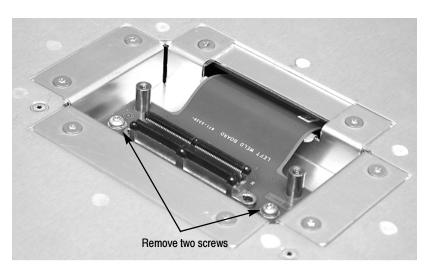

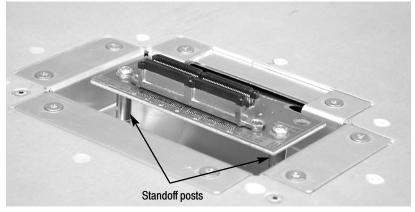

| TLA7Axx Logic Analyzer Merge Procedures                    | E-3         |

| TLA7Lx, TLA7Mx, TLA7Nx, TLA7Px, and TLA7Qx                 |             |

| Logic Analyzer Merge Procedures                            | E-8         |

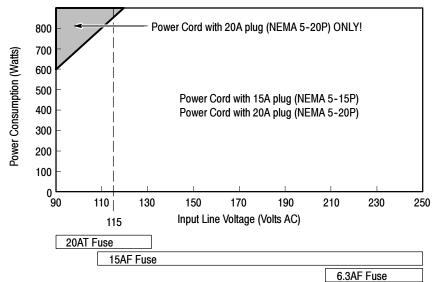

| Appendix F: Power Cord and Line Fuse Requirements for the  |             |

| Benchtop and Expansion Mainframes                          | <b>F-1</b>  |

| Appendix G: Installing Software                            | G-1         |

| Restoring the Hard Disk Image                              | G-2         |

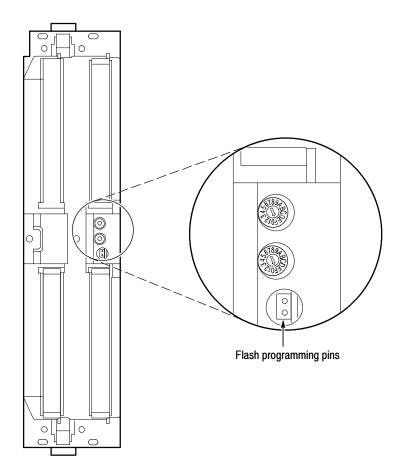

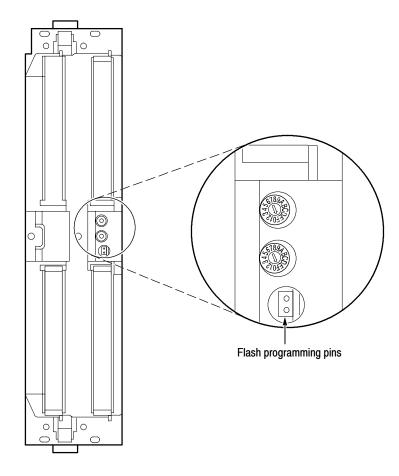

| Flashing the BIOS                                          | G-3         |

| Reinstalling the Hard Disk Image                           | G-11        |

| Reinstalling the TLA Application Software                  | G-16        |

| Reinstalling the Pattern Generator Application Software    | G-17        |

| Installing the Remote Operation Software                   | G-18        |

| Installing the TLAVu Software                              | G-19        |

| Installing the PatGenVu Software                           | G-20        |

| Upgrading or Restoring Firmware                            | G-20        |

| Appendix H: User Service | H-1  |

|--------------------------|------|

| Service Offerings        | H-1  |

| Service Options          | H-2  |

| General Care             | H-5  |

| Module Self Calibration  |      |

| Preventive Maintenance   | H-5  |

| In Case of Problems      | H-8  |

| Repacking for Shipment   | H-19 |

## Glossary Index

# **List of Figures**

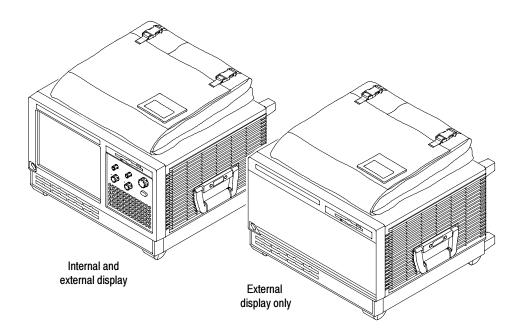

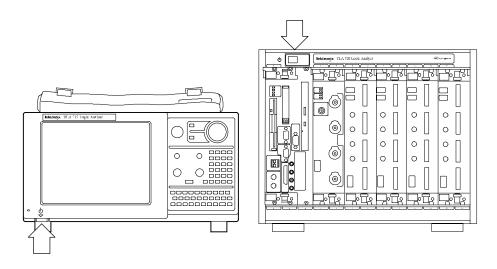

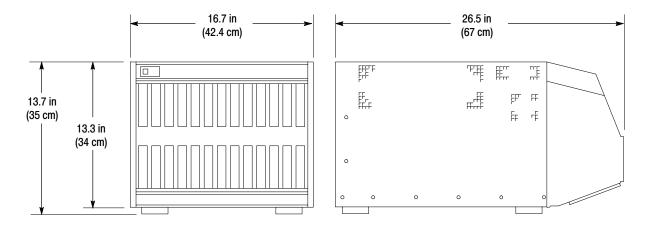

| Figure 1-1: TLA600 series logic analyzers                                                                      | 1-1  |

|----------------------------------------------------------------------------------------------------------------|------|

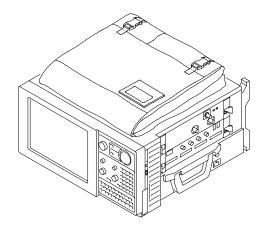

| Figure 1-2: TLA700 portable mainframe                                                                          | 1-2  |

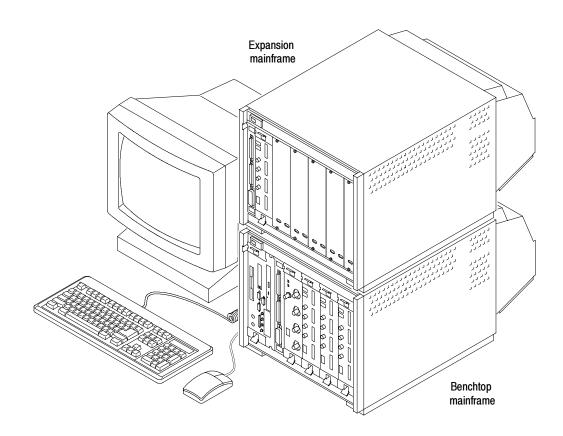

| Figure 1-3: TLA700 benchtop mainframe with an                                                                  |      |

| expansion mainframe                                                                                            | 1-3  |

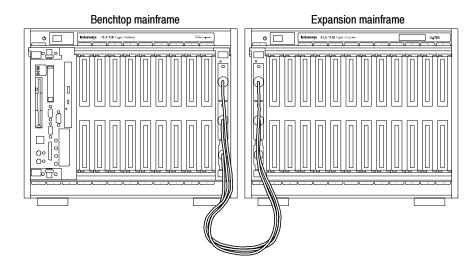

| Figure 1-4: Benchtop mainframe and one expansion mainframe                                                     | 1-6  |

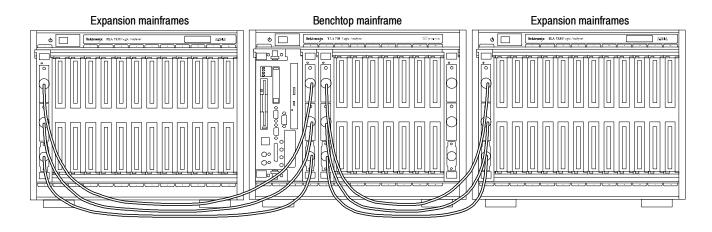

| Figure 1-5: Benchtop mainframe and two expansion mainframes .                                                  | 1-7  |

| Figure 1-6: Portable mainframe shown with two                                                                  |      |

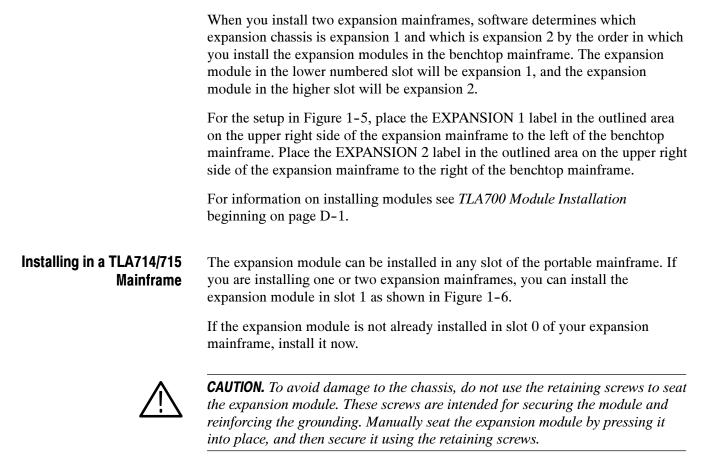

| expansion mainframes                                                                                           | 1-8  |

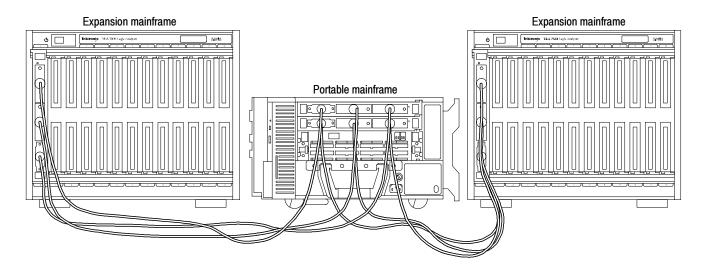

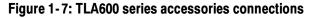

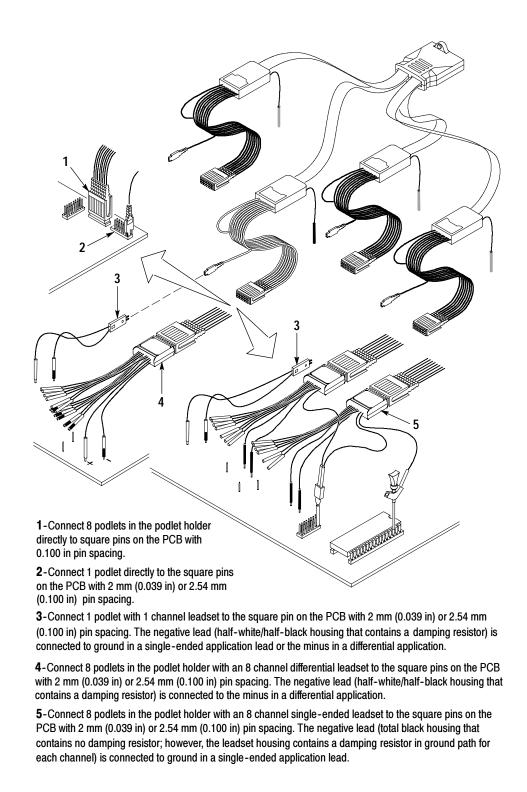

| Figure 1-7: TLA600 series accessories connections                                                              | 1-10 |

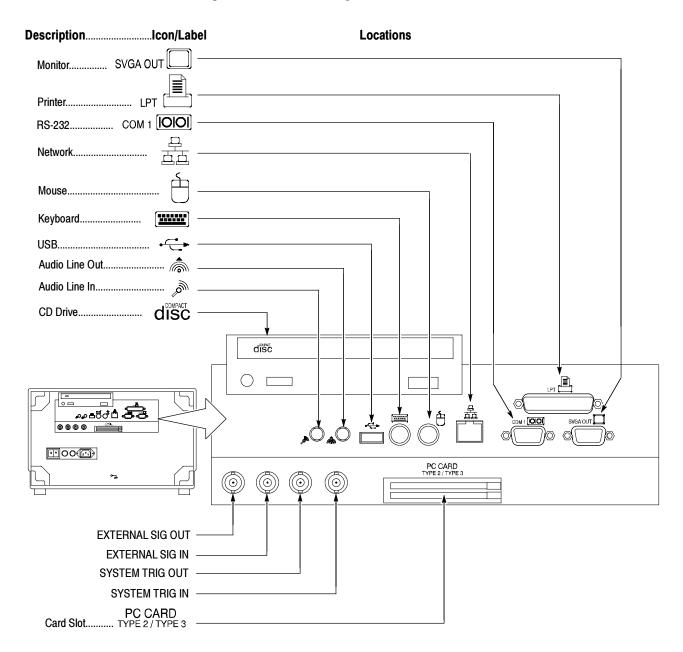

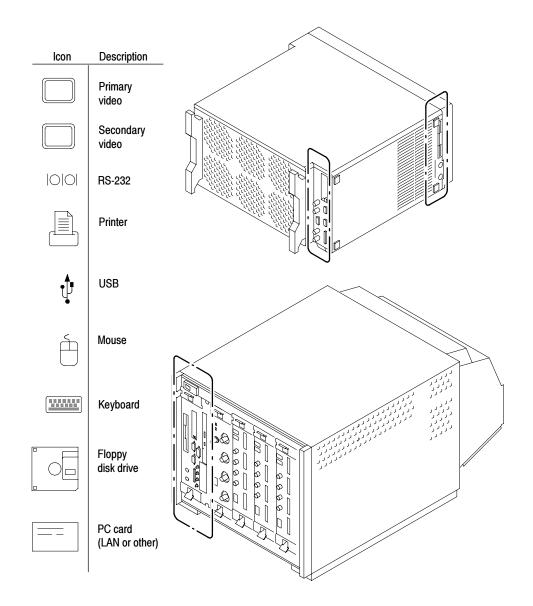

| Figure 1-8: TLA700 series accessories connections                                                              | 1-11 |

| Figure 1-9: Connecting the logic analyzer probes to a                                                          |      |

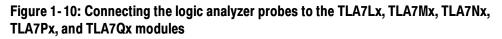

| TLA600 logic analyzer                                                                                          | 1-13 |

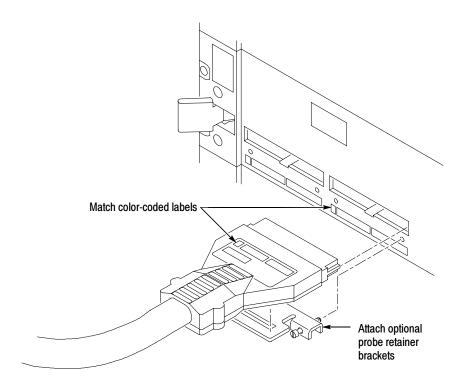

| Figure 1-10: Connecting the logic analyzer probes to the TLA7Lx,<br>TLA7Mx, TLA7Nx, TLA7Px, and TLA7Qx modules | 1-14 |

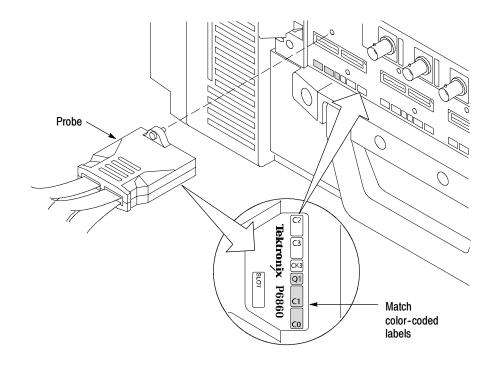

| Figure 1-11: Connecting the logic analyzer probes to the                                                       | 1 17 |

| TLA7Axx module                                                                                                 | 1-15 |

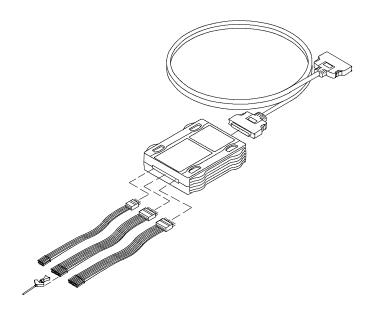

| Figure 1-12: Connecting the pattern generator probes                                                           | 1-16 |

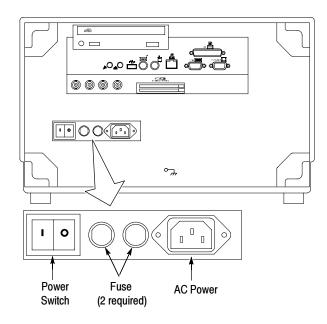

| Figure 1-13: Line fuse and power cord connector locations                                                      | 1-17 |

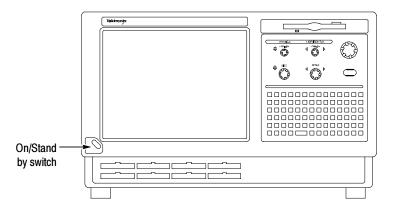

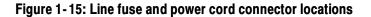

| Figure 1-14: On/Standby switch locations                                                                       | 1-18 |

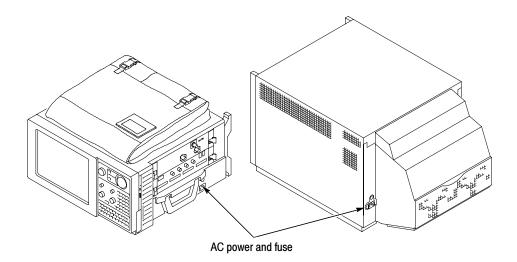

| Figure 1-15: Line fuse and power cord connector locations                                                      | 1-19 |

| Figure 1-16: On/Standby switch locations                                                                       | 1-20 |

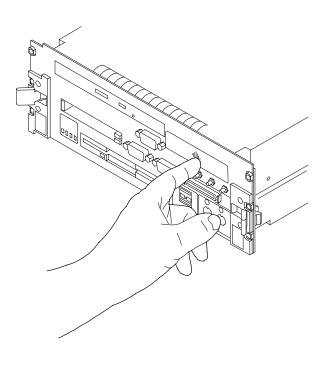

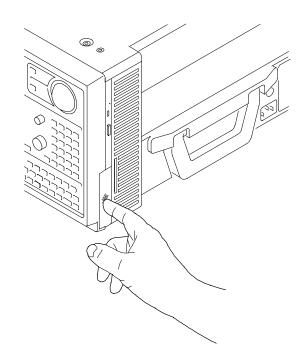

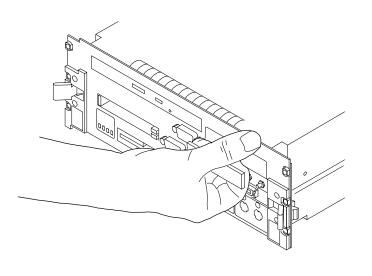

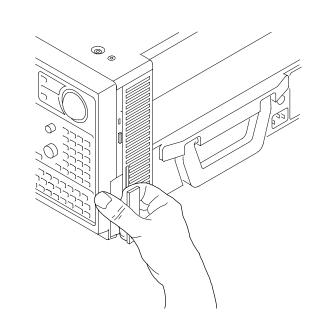

| Figure 1-17: Depress the hard disk drive latch                                                                 | 1-23 |

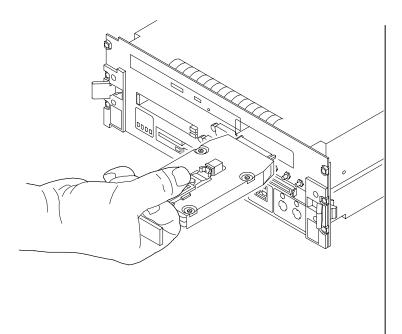

| Figure 1-18: Unlatching the hard disk drive cartridge                                                          | 1-24 |

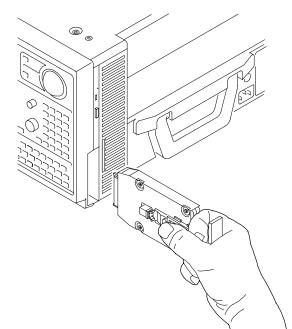

| Figure 1-19: Removing the hard disk drive cartridge                                                            | 1-24 |

| Figure 1-20: Connecting the 17-channel general purpose probe                                                   | 1 41 |

| to the target system                                                                                           | 1-26 |

| Figure 1-21: Connecting the 34-channel P6810                                                                   |      |

| general purpose probe to the target system                                                                     | 1-27 |

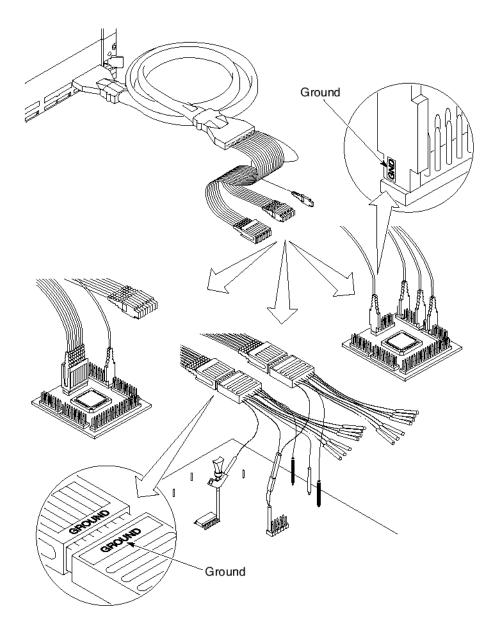

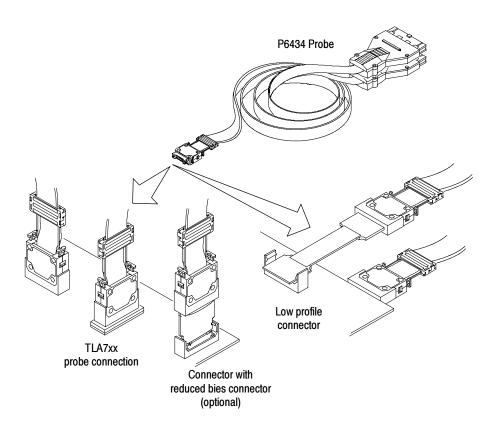

| Figure 1-22: P6434 High-Density Probe connections                                                              | 1-28 |

| Figure 1-23: P6860 High-Density Probe and P6880                                                                |      |

| Differential Probe connections                                                                                 | 1-30 |

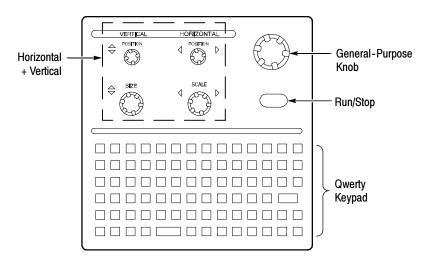

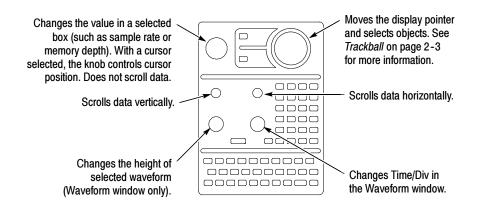

| Figure 2-1: TLA61x/62x Logic analyzer front panel                                                              | 2-1  |

| Figure 2-2: TLA715 Portable mainframe front panel                                                              | 2-2  |

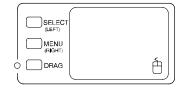

| Figure 2-3: GlidePoint pad                                                                                     | 2-2  |

| Figure 2-4: Trackball                                                                                          | 2-3  |

| Figure 2-5: TLA600 series external connectors                                                                  | 2-4  |

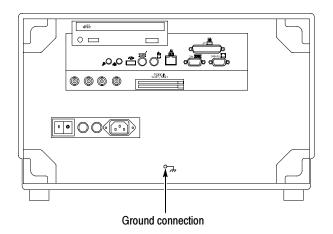

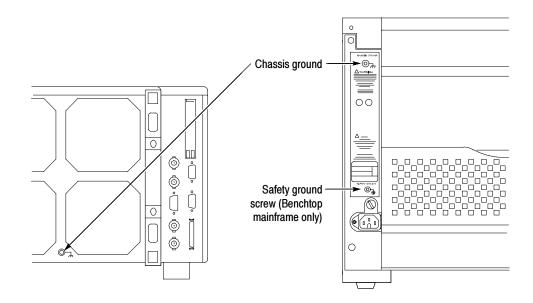

| Figure 2-6: Location of ground connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-5  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

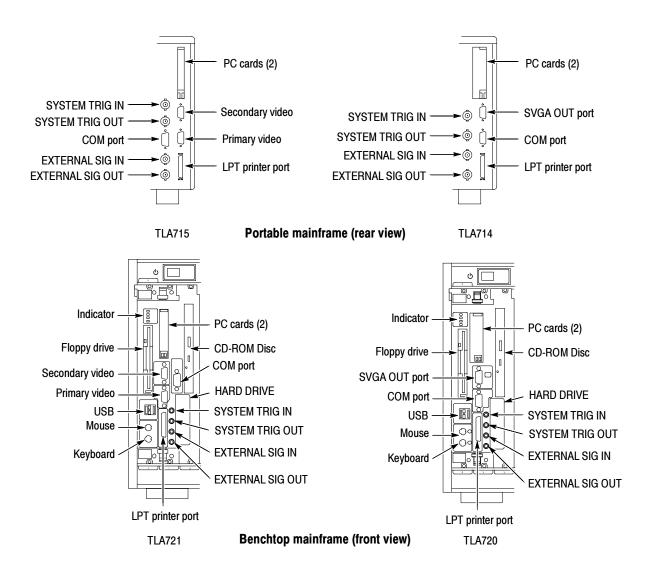

| Figure 2-7: TLA700 series external connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-6  |

| Figure 2-8: Location of ground connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-7  |

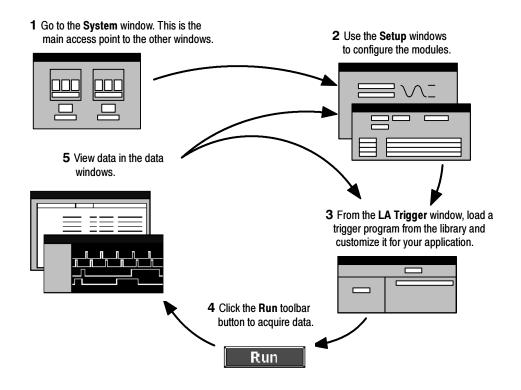

| Figure 2-9: Window usage control flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-9  |

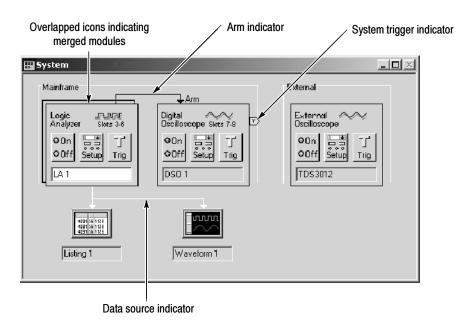

| Figure 2-10: System window on a TLA600 series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-10 |

| Figure 2-11: System window on a TLA700 series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-10 |

| Figure 2-12: LA Setup window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-11 |

| Figure 2-13: DSO Setup window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-12 |

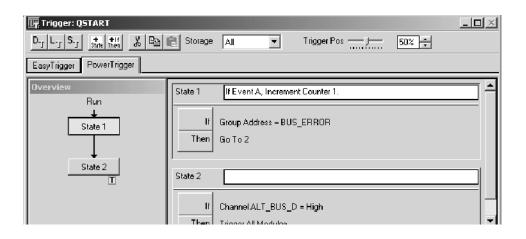

| Figure 2-14: LA Trigger window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-13 |

| Figure 2-15: DSO Trigger window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-13 |

| Figure 2-16: Comparing regular and MagniVu data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-17 |

| Figure 2-17: Using a property sheet to customize the display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-18 |

| Figure 2-18: Window usage control flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-21 |

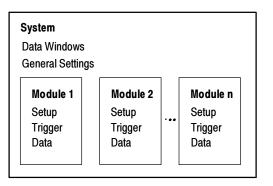

| Figure 2-19: System window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-22 |

| Figure 2-20: Module Setup tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-23 |

| Figure 2-21: Block tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-24 |

| Figure 2-22: Listing window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-25 |

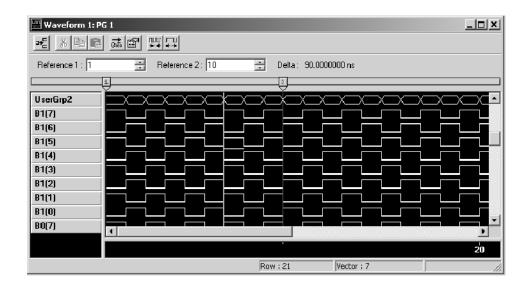

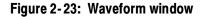

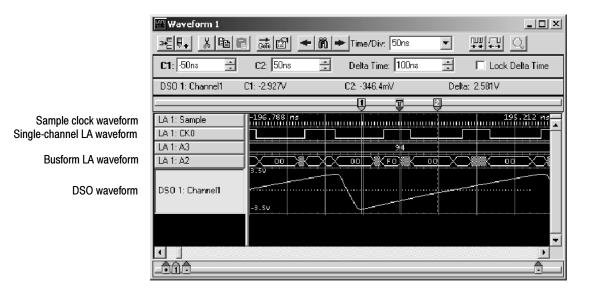

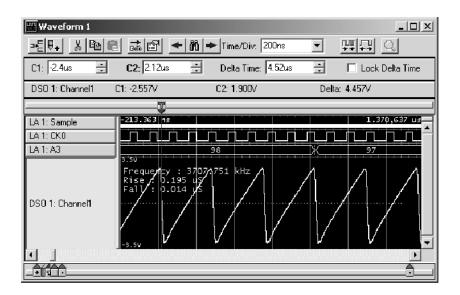

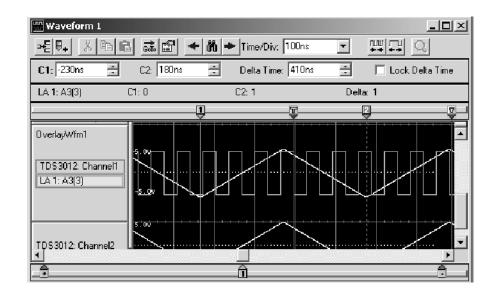

| Figure 2-23:    Waveform window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-26 |

| Figure 2-24: Pattern Generator Run Properties dialog box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-26 |

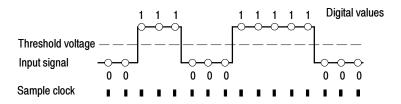

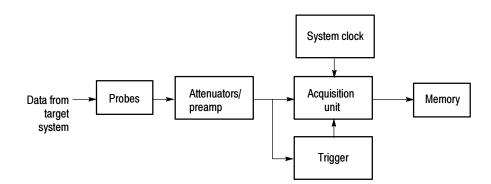

| Figure 2-25: Acquiring a digital signal (LA module)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-27 |

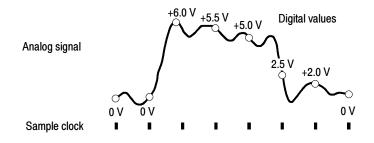

| Figure 2-26: Acquiring an analog signal (DSO module)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-28 |

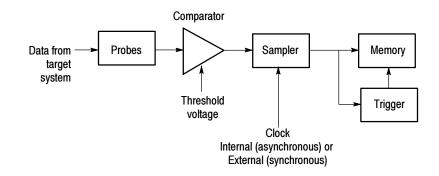

| Figure 2-27: Block diagram of the LA module acquisition and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-28 |

| Figure 2-28: Block diagram of the DSO module acquisition and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-30 |

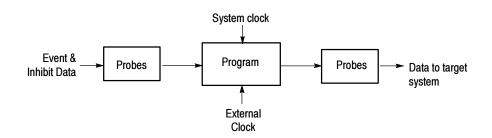

| Figure 2-29: Block diagram of the pattern generator module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-31 |

| Figure 2-30: Logic analyzer physical model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-33 |

| Figure 2-31: Logic analyzer conceptual model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-34 |

| Figure 2-32: Listing data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-35 |

| Figure 2-33: Listing window with analog data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-36 |

| Figure 2-34: Listing data using a microprocessor support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.20 |

| package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-36 |

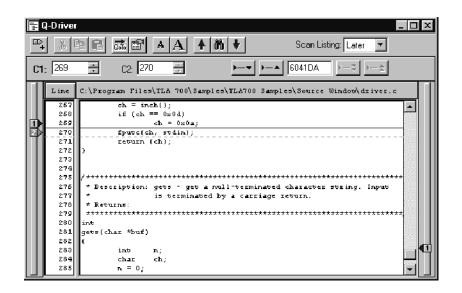

| Figure 2-35: High-level source code         Figure 2-36: Source code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-37 |

| Figure 2-36: Source code viewed as acquired data         Figure 2-27. We figure 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-38 |

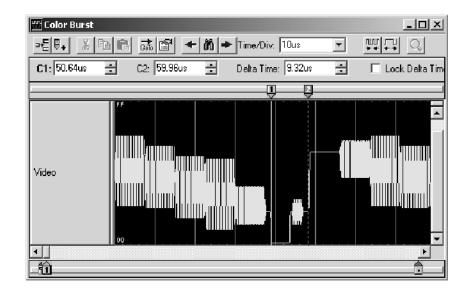

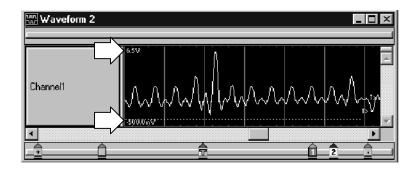

| Figure 2-37: Waveform data           F:         2.29         U.i.         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10)         (1.10) | 2-39 |

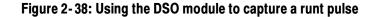

| Figure 2-38: Using the DSO module to capture a runt pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-40 |

| Figure 2-39: LA module sampling resolution         Figure 2-40.41%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-41 |

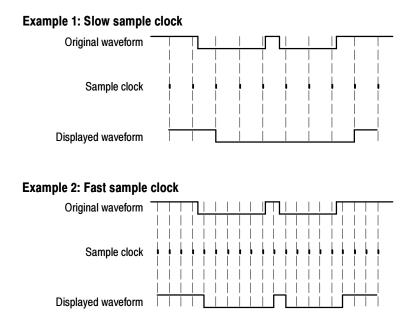

| Figure 2-40: Aliasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-42 |

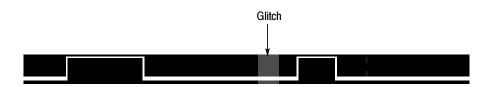

| Figure 2-41: LA module triggering on a glitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-44 |

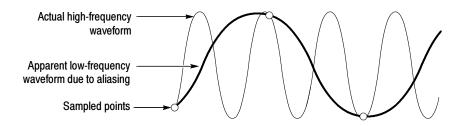

| Figure 2-42: DSO module triggering on a glitch           | 2-44 |

|----------------------------------------------------------|------|

| Figure 2-43: Viewing the performance of code with a      |      |

| Histogram window                                         | 2-45 |

| Figure 2-44: Using color to show memory differences in a |      |

| Listing window                                           | 2-46 |

| Figure 2-45: Defining repetitive setups                  | 2-47 |

| Figure 2-46: Using symbols in a trigger program          | 2-48 |

| Figure 2-47: Waveforms using pattern symbols             | 2-50 |

| Figure 2-48: Listing data using range symbols            | 2-50 |

| Figure 2-49: Symbols dialog box                          | 2-51 |

| Figure 2-50: Load Symbol Options dialog box              | 2-52 |

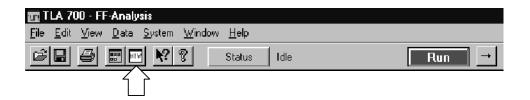

| Figure 3-1: System window                                | 3-1  |

| Figure 3-2: Opening a Waveform window from the           |      |

| System window                                            | 3-2  |

| Figure 3-3: LA module Setup window                       | 3-3  |

| Figure 3-4: Setup window with the QSTART support package | 3-4  |

| Figure 3-5: Sample Suppression dialog box                | 3-5  |

| Figure 3-6: Selecting channels for memory compare        | 3-6  |

| Figure 3-7: Enabling data compare                        | 3-6  |

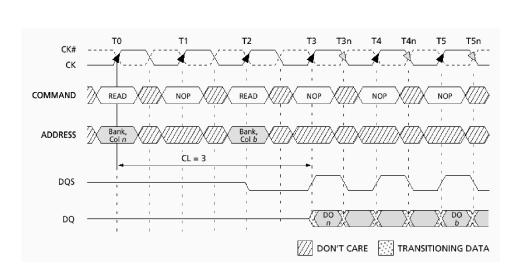

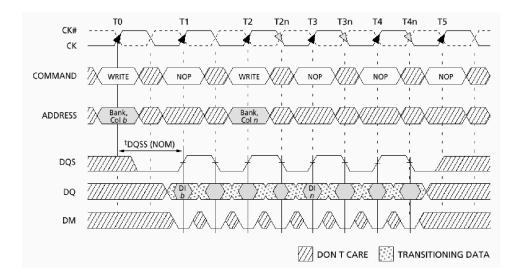

| Figure 3-8: Typical DDR SDRAM consecutive READ bursts    | 3-11 |